x86_64-寄存器详解

说明

这一篇的寄存器来自于Rust-x86_64库总结,讲解在registers下的一些寄存器, 随时更新

寄存器

通用寄存器

| 寄存器名 | 作用 | 谁保存 |

|---|---|---|

| %rax | 返回值 | - |

| %rbx | 被调用者 | |

| %rcx | 参数4 | 调用者 |

| %rdx | 参数3 | 调用者 |

| %rsi | 参数2 | 调用者 |

| %rdi | 参数1 | 调用者 |

| %rbp | 被调用者 | |

| %rsp | 栈顶(指针) | - |

| %r8 | 参数5 | 调用者 |

| %r9 | 参数6 | 调用者 |

| %r10 | 调用者 | |

| %r11 | 调用者 | |

| %r12 | 被调用者 | |

| %r13 | 被调用者 | |

| %r14 | 被调用者 | |

| %r15 | 被调用者 |

还有一个指令寄存器RIP, 不知道放哪就放这了

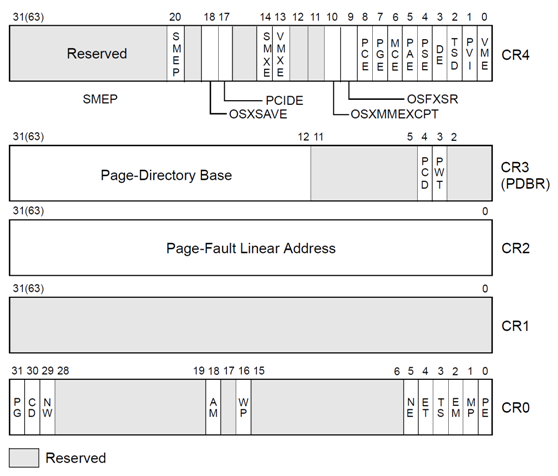

Control Registers

各个寄存器大致的说明:

- CR0: 当前处理器运行的控制标志

- CR2: 发生页面错误时的线性地址

- CR3: 最高级页表的地址(与RISCV中的satp作用差不多)

- CR4: 包含处理器扩展功能的标志位

图片:

CR0

| 位名 | 全称 | 作用(是否的话除特殊说明否则视为bool) |

|---|---|---|

| PE | Protected mode Enable | 是否启用保护模式 |

| MP | Monitor coProcessor | 与TS一起使用, 一起决定是否 触发一个 #NE 错误(?) |

| EM | Emulate coProcessor | 是否能使用 x87与MMX 指令, 如果为1, 则不能使用, 并触发 #NE 错误 |

| TS | Task Switched | 当任务切换时自动置为1 |

| ET | Extension Type | 是否支持 387DX 数学协处理器(Rust注释中这个一般在最近发行的处理器都有) |

| NE | Numeric Error | Enables the native (internal) error reporting mechanism for x87 FPU errors.(注释) |

| WP | Write Protect | 决定S-mode(RING2?)能否写入只能读的page |

| AM | Alignment mask | 用户模式自动对齐 |

| NW | Not Write through | 一般设为0, 在老的CPU用来控制 write-back/write-through 缓存策略 |

| CD | Cache Disable | 关闭一些处理器的缓存 |

| PG | PaGing | 是否开启分页模式, 如果为1则PE bit也需要置为1 |

Cache写机制:(Write-back与Write-through)

- Write through: CPU向cache写入数据时, 同时向memory写入数据, 使得数据保持一致

- Write back: CPU更新cache时, 只将cache标记一下(可能是设为Dirty?), 只有当cache需要更新数据时才更新memory

CR3

- PWT(Page-Level Write through) bit: 设置页表是否使用Write through策略, 0则为Write back

- PCD(Page-Level Cache Disable) bit: 是否关闭页表缓存

CR4

PS:

- 有一些图片内没有, 除了第15位为空, 剩下的可以直接顺序往下数

- FS_GS Base我拆开了, 他的位为16, 没参考官方的, 都是从x86 64中的注释以及名字看的

- 由于位实在有点多, CR4主要是标志一些扩展或者特定的处理器功能是否支持, 所以暂时不写作用了..

- 一些位名的全称为猜的, 看全称能体会意思就好了

| 位名(有一些图片内没有, 直接写Rust中的全称了) | 全称 | 作用 | 备注 |

|---|---|---|---|

| VME | Virtual 8086 Mode Extensions | ||

| PVI | Protected mode Virtual Interrupts | ||

| TSD | TimeStamp Disable | ||

| DE | Debugging Extensions | ||

| PSE | Page Size Extension | ||

| PAE | Physical Address Extension | ||

| MCE | Machine Check Exception | ||

| PGE | Page Global Enable | ||

| PCE | Performance monitor Counter Enable | ||

| OSFXSR | OSFXSR | ||

| OSXMMECPT | OSXMMEXCPT | ||

| UMIP | User Mode Instruction Prevention | ||

| L5_Paging | L5_Paging | Intel only | |

| VMXE | Virtual Machine eXtEnsions | Intel only | |

| SMXE | Safe Mode eXtEnsions | Intel only | |

| FS_GS Base | FS_GS Base | ||

| PCIDE | Process Context IDentifiers Enable | ||

| OSXSAVE | OSXSAVE | ||

| KL | Key locker | Intel only | |

| SMEP | Supervisor Mode Execution Protection | ||

| SMAP | Supervisor Mode Access Prevention | ||

| PK | Protection Key user | ||

| CFE | Control Flow Enforcement | ||

| PKE | Protection Key Supervisor | Intel only |

Model Specific Registers

看了下intel的 volume4..貌似每个处理器的MSR还不一样.. 我直接写一下库中的寄存器以及全称/作用吧

| 名 | 全称/作用 |

|---|---|

| Efer | Extended Feature Enable Register |

| FsBase | [FS].Base Model Specific Register |

| GsBase | [GS].Base Model Specific Register |

| KernelGsBase | KernelGsBase Model Specific Register. |

| Star | 系统调用寄存器 |

| LStar | 系统调用寄存器 |

| SFMask | 系统调用寄存器 |

| UCet | U-mode CET配置 |

| SCet | S-mode CET 配置 |

Efer flags

Efer 寄存器内各个位所代表意义

| 全称 | 作用 | 位 |

|---|---|---|

| System Call Extensions | 启用syscall, sysret指令 | 0 |

| Long Mode Enable | 启动长模式 | 8 |

| Long Mode Active | 表明长模式已经启用 | 10 |

| No Execute Enable | 不能执行的页面保护特性 | 11 |

| Secure Virtual Machine Enable | 启用SVM扩展 | 12 |

| Long Mode Segment Limit Enable | 在64位中启用分段长度限制? | 13 |

| Fast fxsave fxrstor | 64位中将fxsave以及fxrstor指令执行的更快 | 14 |

| Translation Cache Extension | 改变invlpg指令如何操作TLB entries | 15 |

Cet flags

| 全称 | 作用 | 位 |

|---|---|---|

| SS Enable | 启用影子栈(shadow stack) | 0 |

| SS Write Enable | 启用 WRSS{D,Q}W指令 | 1 |

| IBT Enable | 启用indirect branch tracking | 2 |

| IBT Legacy Enable | 启用indirect branch tracking 兼容模式(legacy treatment, 我感觉意思是兼容模式) | 3 |

| IBT no track enable | 启用no-track opcode for indirect branch tracking | 4 |

| IBT Legacy Suppress Enable | 禁用 CET Suppression | 5 |

| IBT Suppress Eanble | 启用 Suppression | 10 |

| IBT Tracked | 只读 | 11 |

系统调用寄存器

Lstar

用于存储syscall的入口函数

Star

未知, rCore x86中设为了(2 << 3 << 48) | (1 << 3 << 32)

SFMask

应该是启用syscall的mask, rCore中设为了0x47700,注释为 TF|DF|IF|IOPL|AC|NT, 日后找到了位的意思会补充

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 sdww0的博客!

评论